# Greyhound

A RISC-V SoC with tightly coupled eFPGA on IHP SG13G2

### About Me - Leo Moser

- Open Source Silicon Advocate!

- Submitted to several Open MPW shuttles

- Master's at Graz University of Technology

- o Greyhound as master's thesis

- Work @ Efabless

- CACE Circuit Automatic Characterization Engine

- magic & netgen bringup for the IHP Open PDK

- IHP OpenLane 2 support → LibreLane!

- Leo @ FOSSi Chat: <a href="https://fossi-chat.org">https://fossi-chat.org</a>

@leo:fossi-chat.org

June 2020: sky130 PDK released

June 2020: sky130 PDK released

Dec 2022: gf180mcu PDK released

- June 2020: sky130 PDK released

- Dec 2022: gf180mcu PDK released

- Since 2023: ihp-sg13g2 PDK released

- IHP SG13G2 BiCMOS

- In active development

- Open MPW tapeout program

- Google-sponsored, Efabless-managed

- MPW-1 to MPW-8, GFMPW-0 to GFMPW-1

- o Initial issues, but chips worked!

Bare dies from MPW-6

- Open MPW tapeout program

- Google-sponsored, Efabless-managed

- MPW-1 to MPW-8, GFMPW-0 to GFMPW-1

- o Initial issues, but chips worked!

- chipIgnite

- \$10,000 per tapeout

- 100 QFN @ up to 15mm²

Bare dies from MPW-6

- Open MPW tapeout program

- Google-sponsored, Efabless-managed

- MPW-1 to MPW-8, GFMPW-0 to GFMPW-1

- o Initial issues, but chips worked!

- chipIgnite

- \$10,000 per tapeout

- 100 QFN @ up to 15mm²

- Tiny Tapeout

- A shared silicon tapeout platform

- Hundreds of projects on a single die

Bare dies from MPW-6

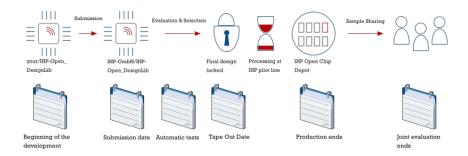

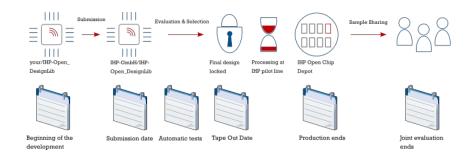

- Free MPW runs funded by BMFTR

- 7 shuttle runs

- IHP SG13G2 / SG13CMOS

- Chips are on loan: IHP Open Chip Depot

- Free MPW runs funded by BMFTR

- 7 shuttle runs

- IHP SG13G2 / SG13CMOS

- Chips are on loan: IHP Open Chip Depot

- ChipFoundry

- ex-Efabless employees

- \$14,950 per tapeout

- o 100 QFN @ up to 15mm<sup>2</sup>

- Free MPW runs funded by BMFTR

- 7 shuttle runs

- IHP SG13G2 / SG13CMOS

- Chips are on loan: IHP Open Chip Depot

- ChipFoundry

- ex-Efabless employees

- \$14,950 per tapeout

- o 100 QFN @ up to 15mm<sup>2</sup>

- wafer.space

- o GF180MCU

- To be announced

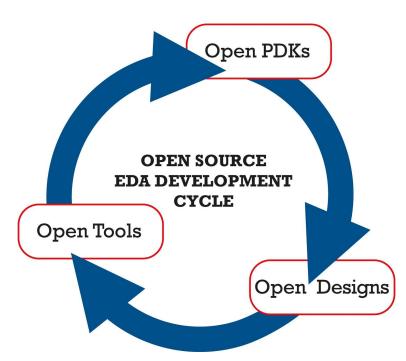

- Revolution in education

- Students can freely access

EDA tools, PDKs, and designs

- Chip design becomes attractive again!

R. Scholz et al., "Update on IHP open source PDK initiative" FSiC2024

# **Introducing Greyhound**

### The Key Points

- RISC-V SoC: CV32E40X

- eFPGA fabric: FABulous

- Custom instruction extension

- Custom peripheral

- Standalone FPGA

- Implemented with LibreLane!

- IHP Open PDK: SG13G2 130nm BiCMOS

- Open Source:

- https://github.com/mole99/greyhound-ihp

- Manufactured at IHP's pilot line

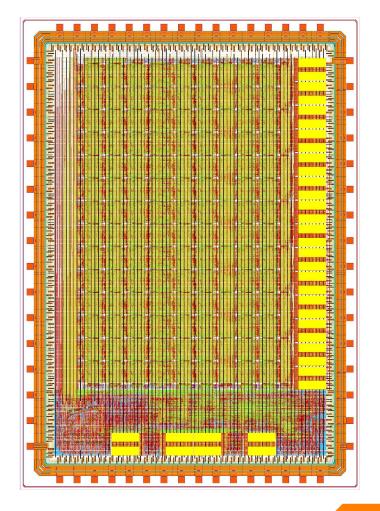

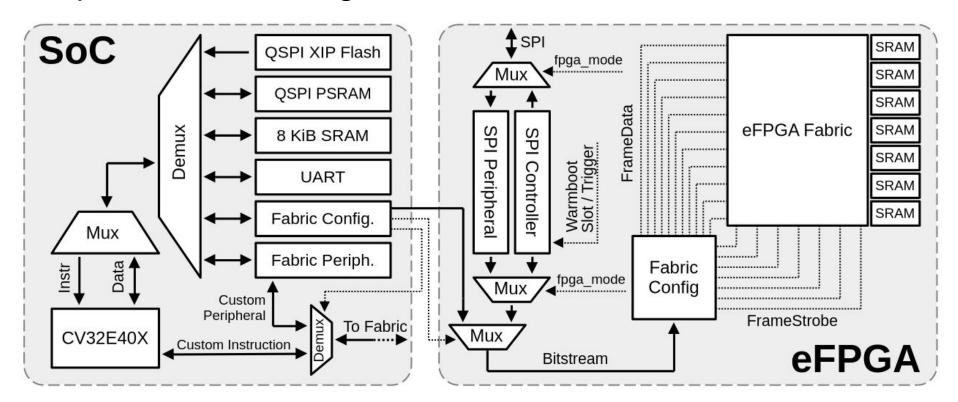

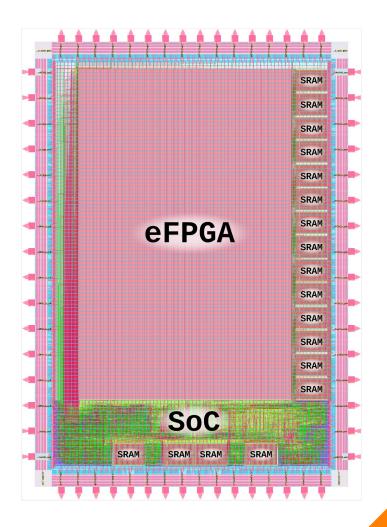

### Top-Level Block Diagram

### System on Chip

- RISC-V core: CV32E40X

- o RV32IMAC

- Zca\_Zcb\_Zcmp\_Zcmt (code-size reduction)

- Zba\_Zbb\_Zbc\_Zbs (bit manipulation)

- o Zicntr, Zicsr, Zihpm, Zifencei

- 8 KiB of built-in SRAM

- QSPI XIP Flash controller

- Cache: 8 lines of 32 bytes, direct-mapped

- QSPI PSRAM controller

- Highly configurable UART

- Configure and access the eFPGA

### FABulous eFPGA Fabric

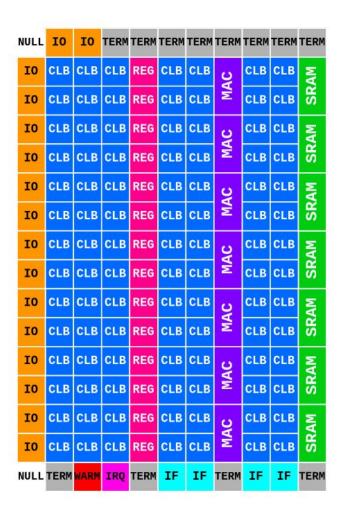

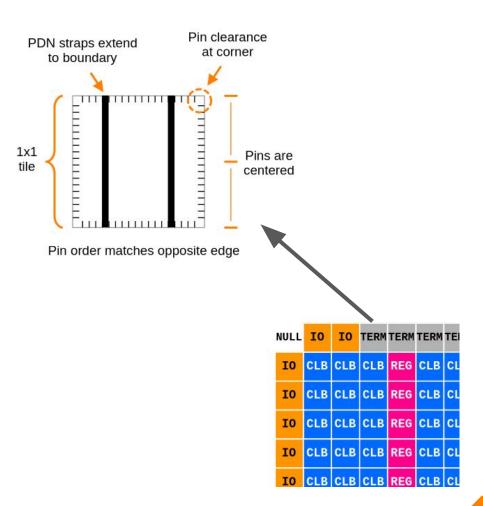

#### FABulous tiles

- o 32 I/Os

- 784 LUT4 + FF (w. carry chain)

- 98 MUX (1×MUX8, 2×MUX4 or 4×MUX2)

- 7 SRAM (1024×32, bit-enable, single-ported)

- 7 MAC (8bit · 8bit + 20bit)

- 14 Register file (32×4, 1w2r)

- 1 Global clock network

#### Custom tiles

- 1 WARMBOOT (16 slots)

- 1 CPU\_IRQ (4×IRQs)

- 4 CPU\_IF (CPU/SoC)

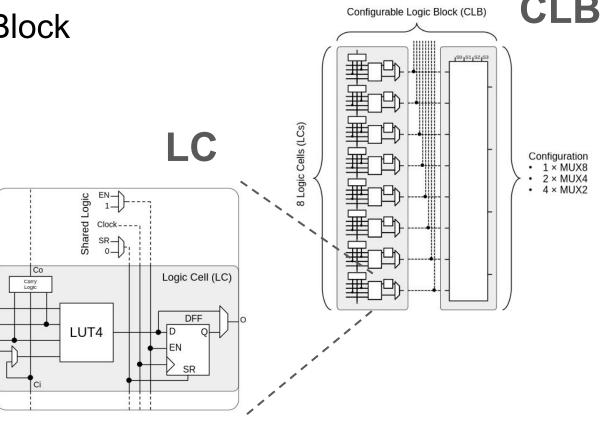

### Configurable Logic Block

- One CLB consists of

- o 8 Logic Cells

- o 1 Multiplexer

- One LC consists of

- Carry chain

- o LUT4

- o D-FF

- Shared Logic

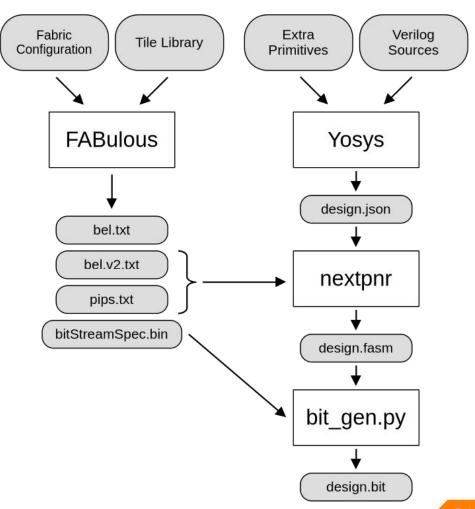

### User Designs

- Yosys & nextpnr toolchain

- + fasm python package

- RISC-V designs

- QERV (4-bit variant)

- FazyRV (1-bit variant)

|            | LC usage  |           |

|------------|-----------|-----------|

| FPGA       | QERV      | FazyRV    |

| Greyhound  | 720 (92%) | 754 (96%) |

| iCE40 UP5K | 709       | 634       |

LC usage comparison

## **Physical Implementation**

### FABulous Plugin

- Integrates into LibreLane

- Custom steps / flows

- FABulousTile

- FABulousFabric

- Custom configuration variables

- FABULOUS\_TILE\_LIBRARY

- FABULOUS\_FABRIC\_CONFIG

- FABULOUS\_TILE\_SIZES

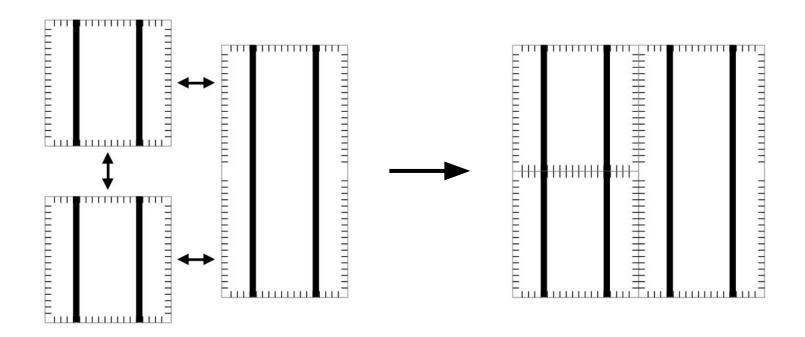

### Stitching the Fabric

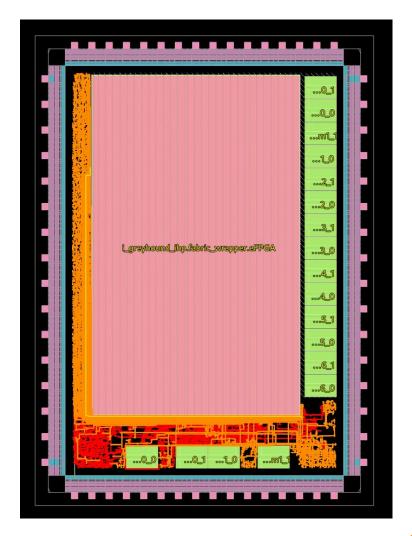

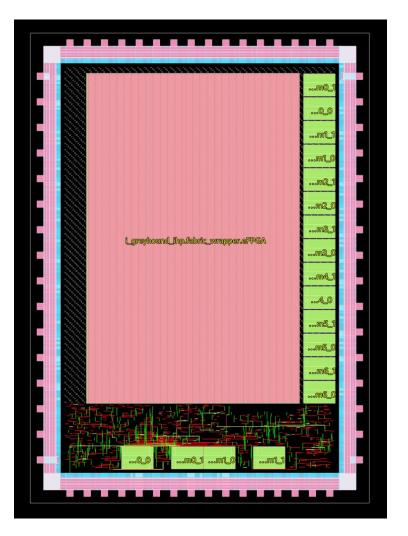

### Implementing the Chip

- Proved to be difficult!

- Hold violations everywhere?

- o RC-estimate vs. SPEF extraction

- Clock tree was skewed

- Workaround: Limit core area

- Solution:

- Bugfix in OpenROAD

- Vertical layer resistance in clock net was not considered

- Thanks Donn!

### Implementing the Chip

- Proved to be difficult!

- Hold violations everywhere?

- o RC-estimate vs. SPEF extraction

- Clock tree was skewed

- Workaround: Limit core area

- Solution:

- Bugfix in OpenROAD

- Vertical layer resistance in clock net was not considered

- Thanks Donn!

## Verification

### Verification - Will it work?

- Testbenches with cocotb!

- Simulations:

- SoC on its own: RTL & GL 🔽

- Fabric on its own:

RTL

- Chip top-level: RTL & GL\* 🗸

- Abstract LVS

- Minimal DRC

<sup>\*</sup>only SoC, fabric is always RTL

### Verification - Will it work?

- Testbenches with cocotb!

- Simulations:

SoC on its own:

RTL & GL

Fabric on its own:

RTL

Chip top-level:

RTL & GL\* 🗸

Abstract LVS

Minimal DRC

| corner              | frequency |

|---------------------|-----------|

| nom_fast_1p32V_m40C | 85 MHz    |

| nom_typ_1p20V_25C   | 55 MHz    |

| nom_slow_1p08V_125C | 34 MHz    |

STA results for the SoC

\*only SoC, fabric is always RTL

### Verification - Will it work?

- Testbenches with cocotb!

- Simulations:

o SoC on its own: RTL & GL

Fabric on its own:

RTL

○ Chip top-level: RTL & GL\* 🔽

- Abstract LVS

- Minimal DRC

| corner              | frequency |

|---------------------|-----------|

| nom_fast_1p32V_m40C | 85 MHz    |

| nom_typ_1p20V_25C   | 55 MHz    |

| nom_slow_1p08V_125C | 34 MHz    |

STA results for the SoC

Fingers crossed 🤞

<sup>\*</sup>only SoC, fabric is always RTL

### Acknowledgements

- Graz University of Technology

- Tobias Scheipel

- Meinhard Kissich

- FABulous Team

- Heidelberg University

- University of Manchester

- Open Source Team @ IHP

- Tim Edwards @ Open Circuit Design

- BMFTR: FMD-QNC (16ME083)

### The Future of Greyhound

- Next revision

- Update to LibreLane

- Newer OpenROAD

- Better antenna / jumper insertion

- Use the new standard cells

- Future revision?

- BRAM instead of SRAM

- Better custom instructions

- More clock domains

- Timing annotation

- Excited about the future!

## Questions?

https://github.com/mole99/greyhound-ihp